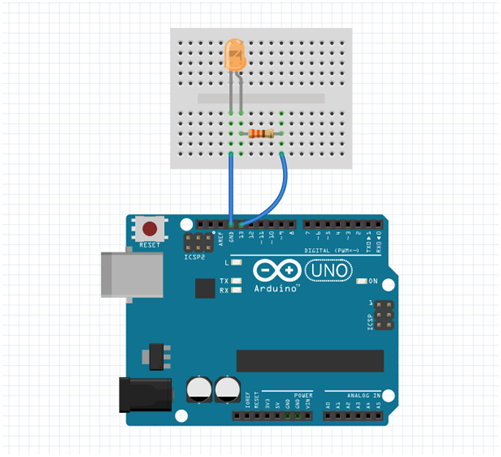

아두이노 – 나도 해보는 LED 깜빡이기 [아두이노 강좌] 02. LED 밝기 변경하기 회로를 다음과 같이 구성합니다. 스케치툴을 키고 다음같이 입력 후 void setup() { // put your setup code here, to run once: pinMode(13, OUTPUT); } void loop() { // put your main code here, to run repeatedly: digitalWrite(13, HIGH); delay(1000); digitalWrite(13, LOW); delay(1000); } 1번 버튼과 2번 버튼을 차례로 누른 뒤 아두이노를 보니까 LED가 잘 깜빡이네요.. 여기서 함수 설명 pinMode() : 디지털 핀의 모드를 출력 또는 입력으로 설정하는..