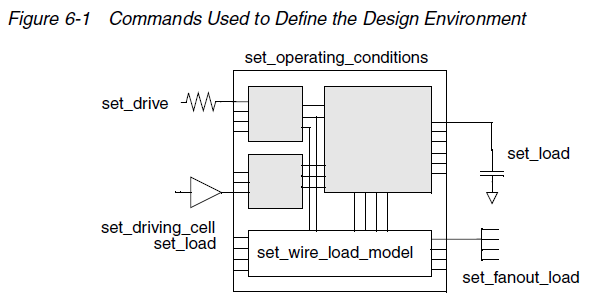

Design Compiler User Guide Chapter 6을 제가 읽으면서 정리한 내용입니다. • Defining the Operating Conditions • Defining Wire Load Models • Modeling the System Interface • Setting Logic Constraints on Ports • Specifying Power Intent • Support for Multicorner-Multimode Designs Defining the Operating Conditions Operating Conditions에는 다음 3가지가 있다. 1. 온도 변화 2. 공급 전압 변화 3. 공정 변화 대부분의 techonology library에는 미리 정의된 opera..